Fault-Tolerant Quantum Computing Is Near: IBM, QuEra Accelerate Timelines

Published Nov 18, 2025

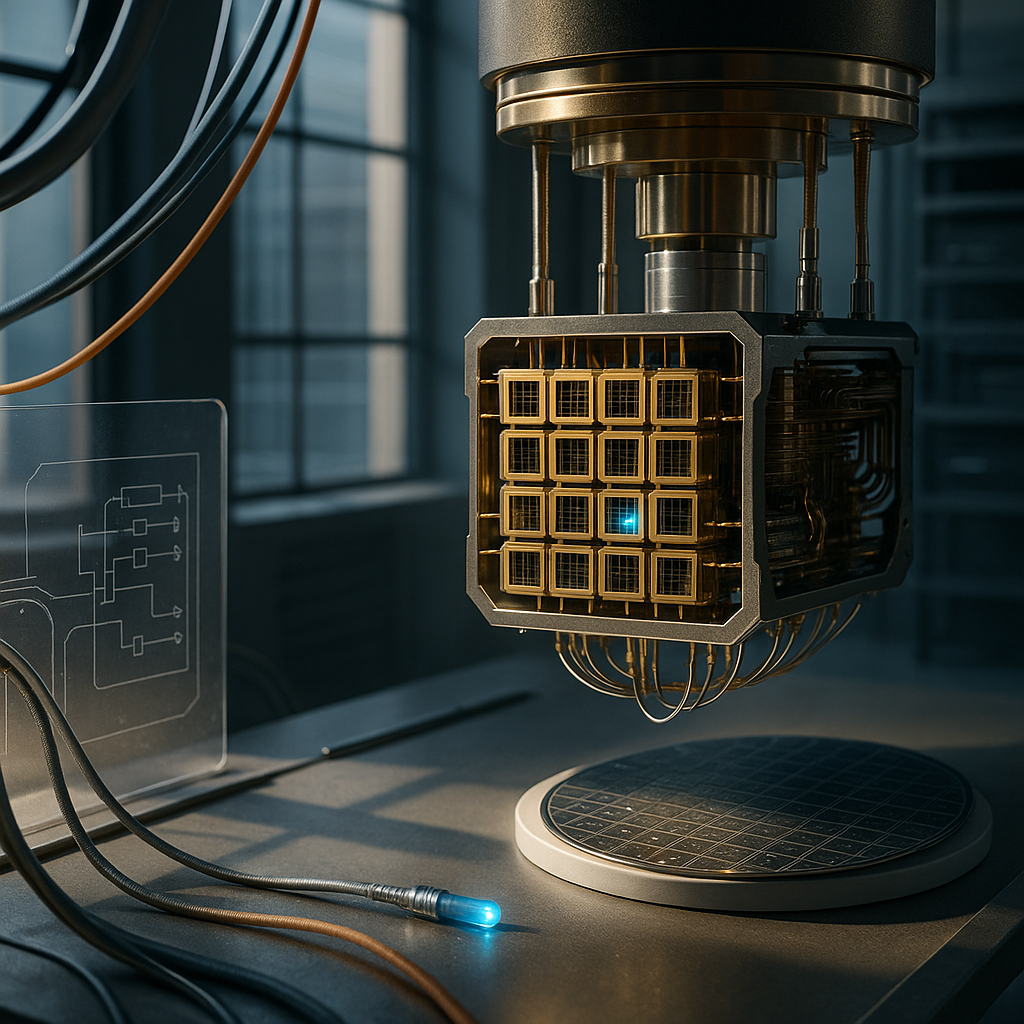

Think fault‐tolerant quantum is decades away? Mid‐November 2025 developments say otherwise, and here’s what you need fast: on 2025‐11‐12 IBM unveiled Nighthawk (120 qubits, 218 tunable couplers, 30% more circuit complexity) and Loon (hardware elements for fault tolerance), while IBM’s qLDPC decoders ran 10× faster, dynamic circuits gained 24% accuracy, and error mitigation cut some costs by >100×. QuEra (with Harvard/Yale) published in Nature a low‐overhead fault‐tolerance method that uses one syndrome extraction per logical layer, slashing runtime overhead. Why it matters: these shifts move verified quantum advantage toward 2026 and realistic fault tolerance toward a 2029 Starling target (confidence ~80%). Watch quantum‐advantage demos, logical vs. physical error rates, qLDPC adoption, fabrication/yield, and decoder latency (<480 ns) as immediate next indicators.